今天繼續延續昨天的主題吧,培養一個好的coding習慣真的是非常重要,這兩天還特地翻一下當初寫的code,要不是事先知道題目,還真的不知道自己在寫什麼,不過翻翻以前寫的作業才發現自己進步許多,同一個主題每次寫都會有不一樣的想法,所以今天分享的第一項就是:

-適時地下註解

這應該也是每一種程式都該培養的,就像我偶爾會回頭翻一下以前寫的程式,如果註解下得好,要回頭看就不難,但如果沒下任何註解,變數名稱又亂取的話真的是看了很頭疼,最近我除了會下註解,還會把電路的波形圖畫出來存到子目錄底下,方便回頭看時可以順便看一下波形動態.

-適時地括弧

即使知道運算子的優先權,不過如果用括弧括起來表達能力會比較強,像是:

a <= a + 1 << 2

a <= (a + 1) << 2

上面這兩行比較起來,下面比較能一目了然要先做什麼事,上面那行還要先想一下優先權.這樣表達能力就有差了,

接下來大家來看一下以下這兩行程式碼:

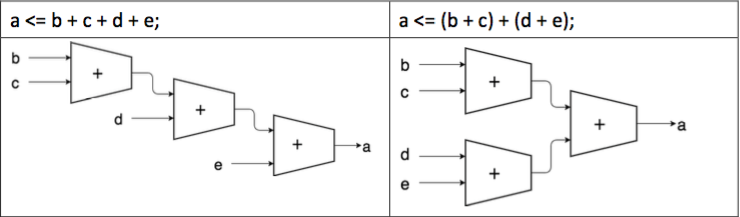

a <= b + c + d + e;

a <= (b + c) + (d + e);

看起來好像沒差,不過當電路合成完時卻會長不一樣,如果合成器沒有幫你把電路優化的話.

不知道看到這樣的比較大家有沒有感覺出來有什麼不同,不同在於左邊那樣寫要經過三個加法器的時間才做完,右邊則是經過兩個加法器就做完,使用的資源一樣卻會有不一樣的運算速度,所以適時的使用括弧也能優化你的電路喔.

-使用FSM

之前在分享有限狀態機(Finite State Machine)時就跟大家說過,多多使用FSM應用在較為複雜的電路,一方面好控制電路,一方面也好找bug,這邊提醒大家一下,使用FSM時也不要把你全部的state擠在同一個FSM,而是根據不同的應用去驅動各個FSM,像是前幾天的費伯納西數列運算電路,如果妳寫完了要利用uart印出來的話,應該利用一個FSM控制費伯納西數列的運算,之後再利用一個FSM去控制uart的行為,而不是全部擠在一個FSM,

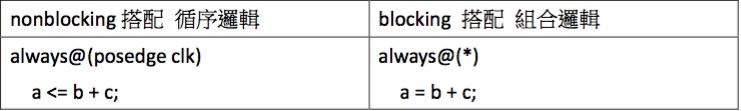

-blocking搭配 循序邏輯

-nonblocking 搭配 組合邏輯

這存粹是我自己的習慣,因為我也有看過有人不是這樣搭配的,用個表個示意一下:

之前也有提過,其實較為複雜的電路是由組合邏輯跟循序邏輯組合而已

always@(*)begin

a = b + c;

d = a + e;

end

always@(posedge clk)

temp <= d;

像上面這樣,做完一連串的組合邏輯運算完再用循序邏輯去存起來,上面也可以直接寫成下面這樣:

always@(posedge clk)

temp <= b + c + e;

意思一樣,就看大家怎樣寫比較習慣.

-化複雜為簡單

這個真的需要許多經驗及技巧,往後幾天我會分享幾個我所知道的電路,這邊稍為提一點,像是乘法跟除法這種複雜運算能不用就別用,看能不能利用其他方式代替,像是乘2的幂次方就可以用位移代替:a <= b * 4;可以寫成a <= b << 2,除法也是,取餘數的話像是a <= b % 16; 可以寫成 a <= b[3:0]這樣,這都是一些小技巧.

今天先到這,往後有想到什麼會再跟大家分享.